Содержание

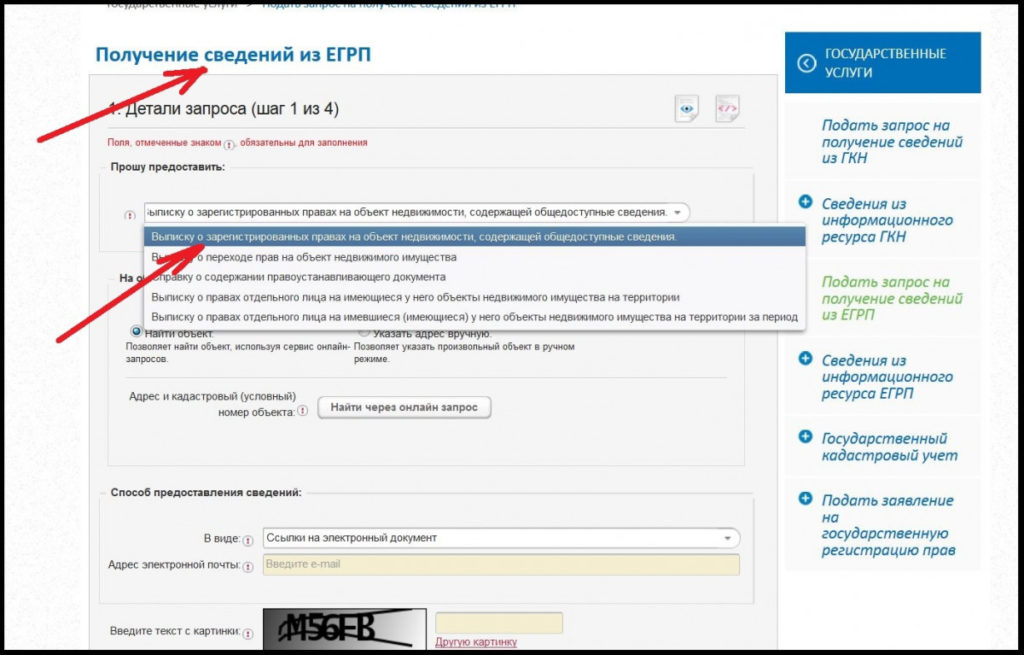

Выписка из ЕГРП через Госуслуги || KadastrMap.com

Найдите свой объект недвижимости

Поиск работает по адресу (используйте выпадающие подсказки), по кадастровому номеру, вручную на карте.

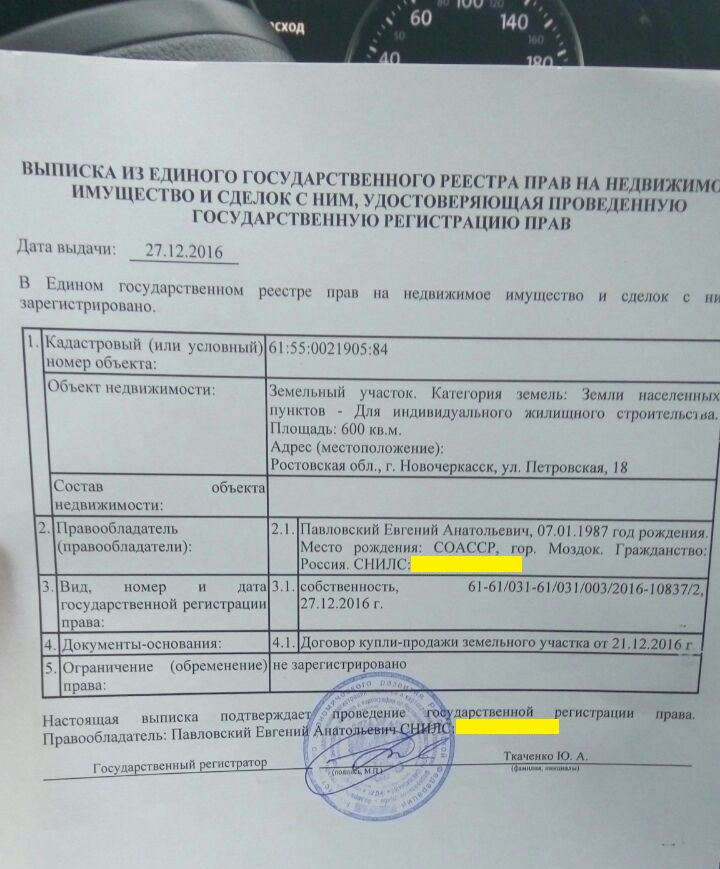

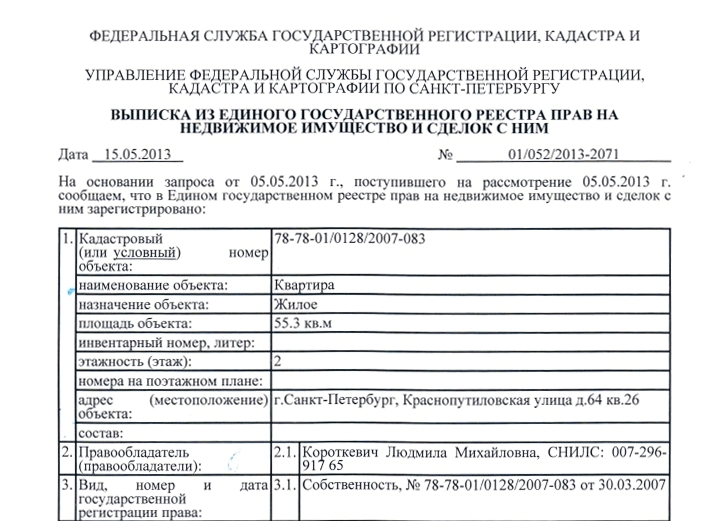

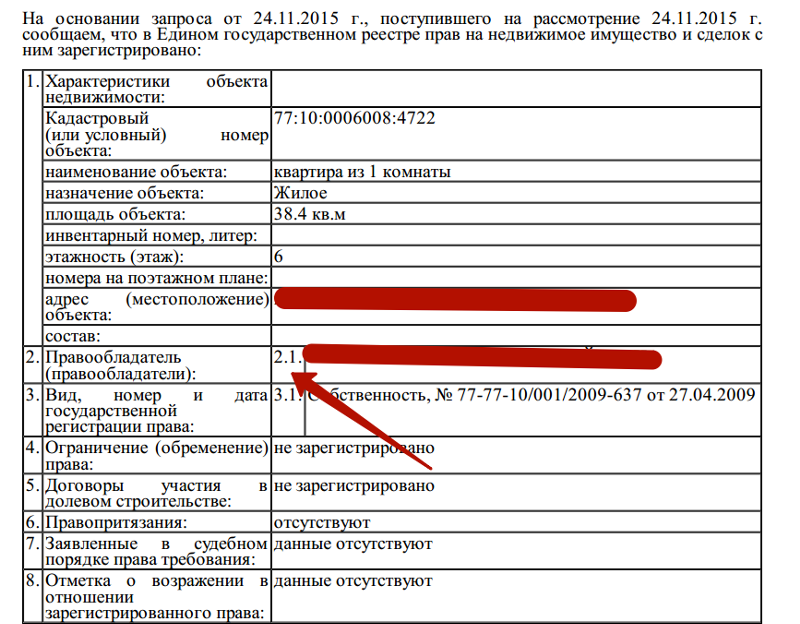

В законе также определена конечная стоимость для лиц, которые будут заказывать документ выписка из ЕГРП через Госуслуги. Согласно положениям закона, для физических лиц, а также для представителей государственных органов власти, установлена государственная пошлина выписки ЕГРН за один субъект недвижимости. Отметим, что полный перечень тарифов и ценообразования определён соответствующим положением в действующем Приказе Минэкономразвития России от 10.05.2016 N 291 (обновлённая редакция от 09.12.2016) «Об установлении размеров платы за предоставление сведений, содержащихся в Едином государственном реестре недвижимости» (документ прошёл регистрацию в соответствующем подразделении Минюста России 21. 07.2016 № 42937).

07.2016 № 42937).

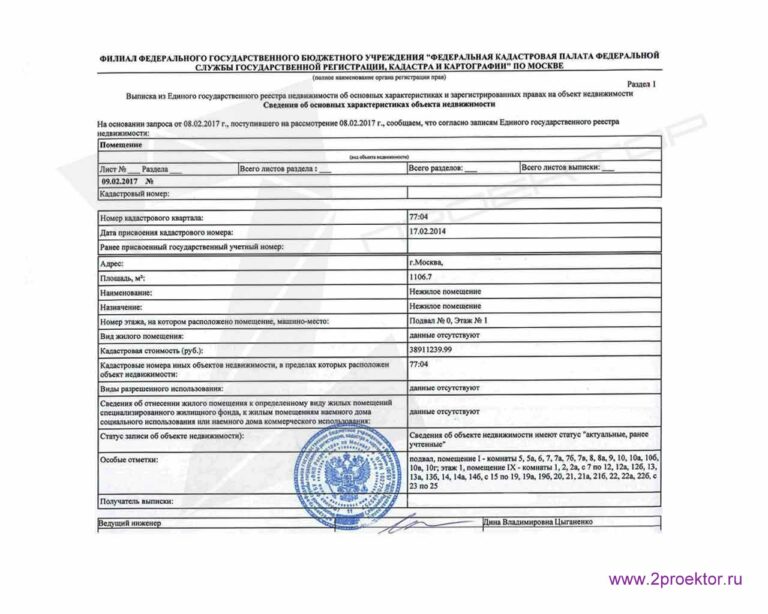

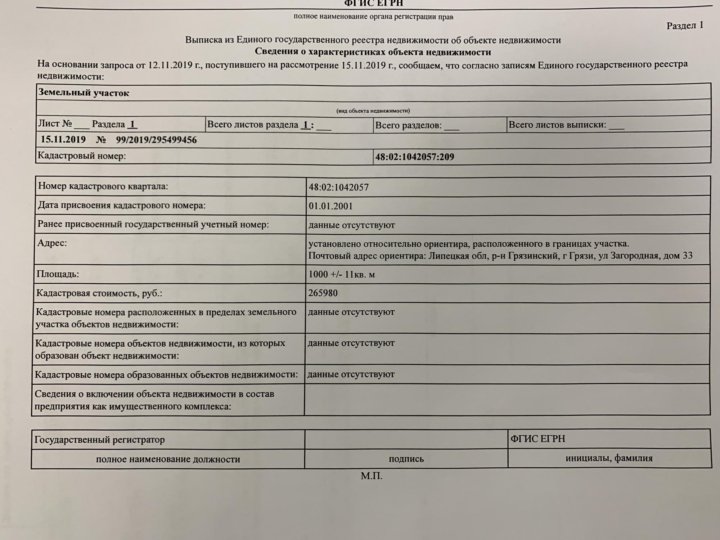

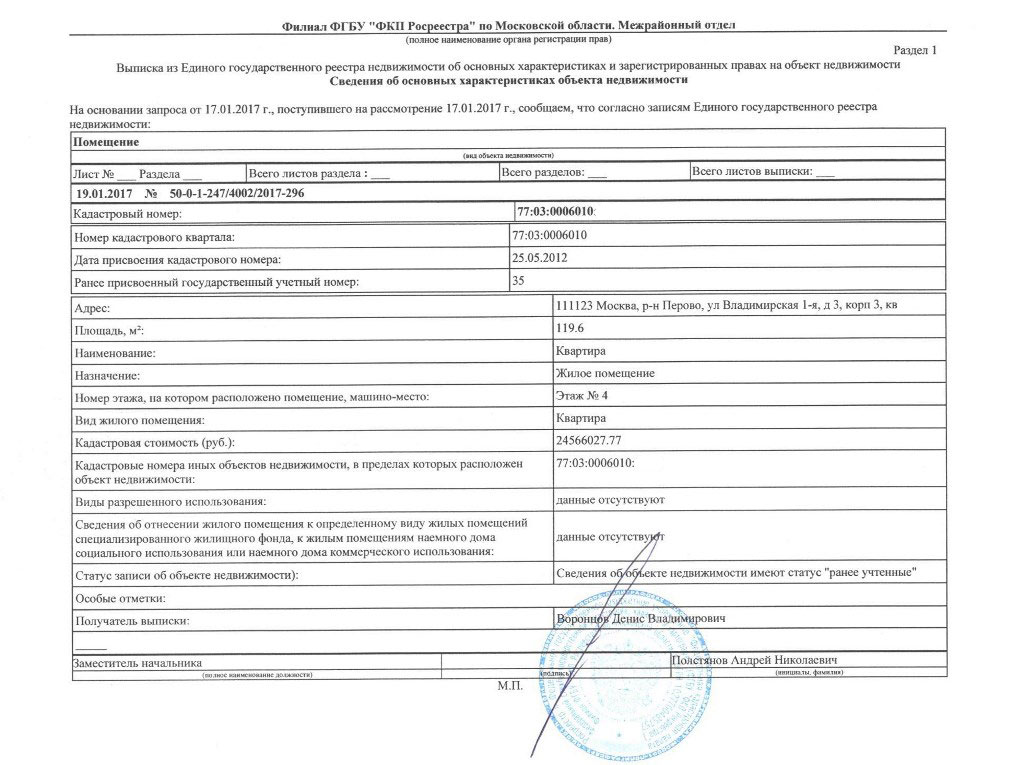

Заметим, что теперь кадастровые данные и характеристики в полном формате отсутствуют в выписке ЕГРП. Чтобы получить исчерпывающую информацию, потребуется заказать Кадастровый паспорт (полная выписка ЕГРН) с графической частью имущественного права, где раскрывается подробная база данных об интересующем вас объекте права.

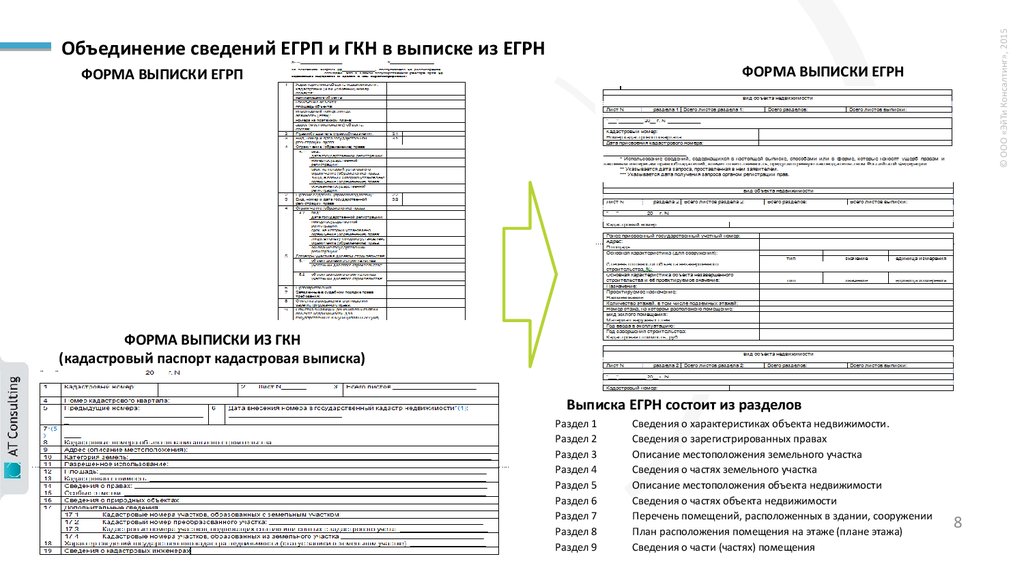

Замена выписки из ЕГРП на выписку из ЕГРН произошла на основании нового ФЗ-218, причём отменены также кадастровые паспорта и свидетельства о госрегистрации. Все сведения в ранее указанных документах перенесены в выписку из ЕГРН.

Заказать аналоговую выписку из ЕГРП Госуслуги и посмотреть образцы документов вы можете здесь.

Изменится также форма выдачи выписки ЕГРН в обновлённом варианте из Росреестра, которая будет иметь совершенно новый вид.

- Информационный блок о субъекте имущественного действия, в том числе его цена в виде кадастровой стоимости.

- Если в качестве предмета выступает земельный надел, вносятся все данные о постройках, которые находятся на данном участке.

- Полная информационная база правовладения на конкретный объект – кто есть правообладатель, какие обременения существуют, и прочие данные.

- Карта обременения (с подробной фиксацией сведений) объекта со всеми данными.

- Информационный блок о притязаниях на предмет недвижимости.

Законом установлены предельные сроки получения электронной или бумажной выписки ЕГРН. При прямом обращении в Росреестр, срок определён 3 рабочих дня, через сервис МФЦ, срок определён 5 рабочими днями.

В законе определён полный перечень лиц, для которых имеется возможность и право для заказа и получения документа выписка из ЕГРП через Госуслуги из общей базы данных Росреестра. Законодатель разработал статью №62 к закону №218.

Напомним, что с 15 июля 2016 года полностью прекращена выдача Свидетельства о регистрации имущественного права, теперь вместо этого документа собственник и правообладатель получает новую выписку ЕГРП (теперь это будет выписка ЕГРН).

Как получить выписку из ЕГРП через Госуслуги и не только

На нашем сайте вы можете подробно узнать информацию про кадастровый паспорт что за документ, и заказать электронный или бумажный вариант выписки ЕГРН в открытом доступе. Оба варианта имеют равную юридическую силу и принимаются всеми заинтересованными силами в качестве официальных документов.

В стоимость услуги включена государственная пошлина, предусмотренная для операции получения выписки из Росреестра.

Получить полную информацию о вашем объекте недвижимости

Получить информацию об вашем объекте

Другие статьи

Получить кадастровый паспорт онлайн в Росреестре

Заказ выписки из ЕГРП

Статьи на тему

Кадастровый паспорт сделать срочно

Многие из нас знают, как дорог каждый день, когда под рукой нет необходимого пакета документов, в частности, для имущественного права — квартиры, комнаты, гаража, земельного участка нужно кадастровый паспорт сделать срочно в день обращения через специальную форму на нашем сайте. Основная функция…

Основная функция…

Получить кадастровый паспорт онлайн

Получить кадастровый паспорт онлайн

О том, стоит ли получить кадастровый паспорт онлайн, бытует множество мнений. И те, которые заказывали указанную услугу, только положительно отзываются об этом. Почему? Испытав на себе всю простоту обработки документов, уже не хочется вдаваться в…

Где заказать кадастровый паспорт на квартиру?

Где заказать кадастровый паспорт на квартиру? Как можно решить вопрос с получением кадастрового паспорта, который необходим как основной документ любого имущественного права на территории России. Для этих целей вам необходимо заказать кадастровый паспорт, который выдаёт официальный орган в лице…

Выписки из ЕГРН — Регистрация недвижимости, кадастровый учет, выписка из ЕГРП, кадастровый паспорт

- Главная

- Получение документов org/Breadcrumb»>Выписки из ЕГРН

Предоставление сведений, содержащихся в ЕГРН —

Едином государственном реестре недвижимости

REG-KADASTR оказывает помощь в получении официальных документов и сведений из ЕГРН.

Документы предоставляет Федеральная служба государственной регистрации кадастра и картографии – РОСРЕЕСТР.

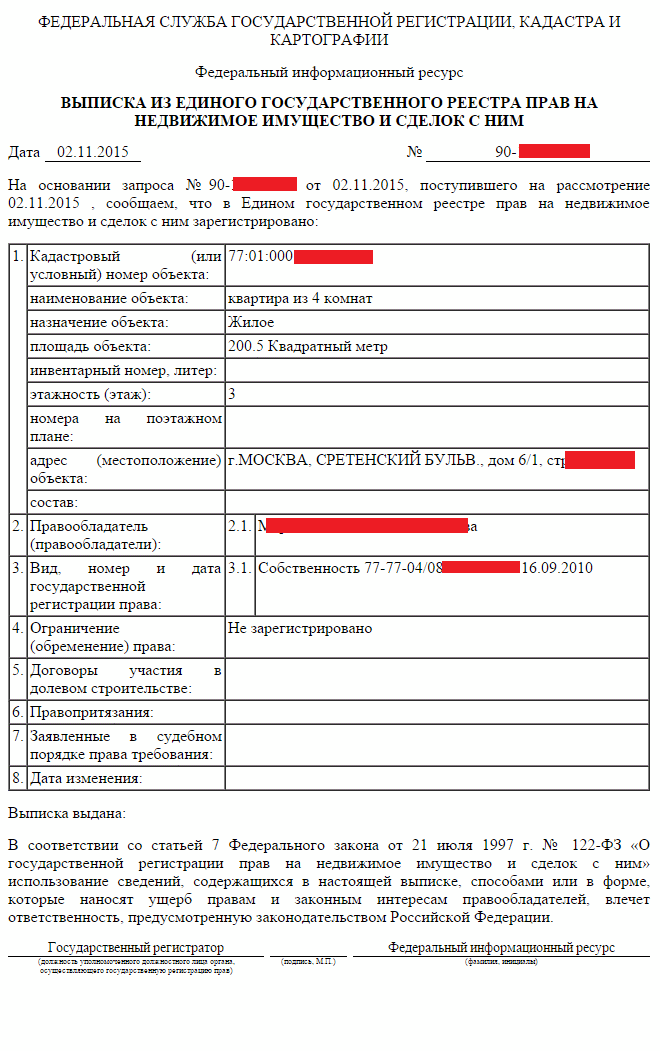

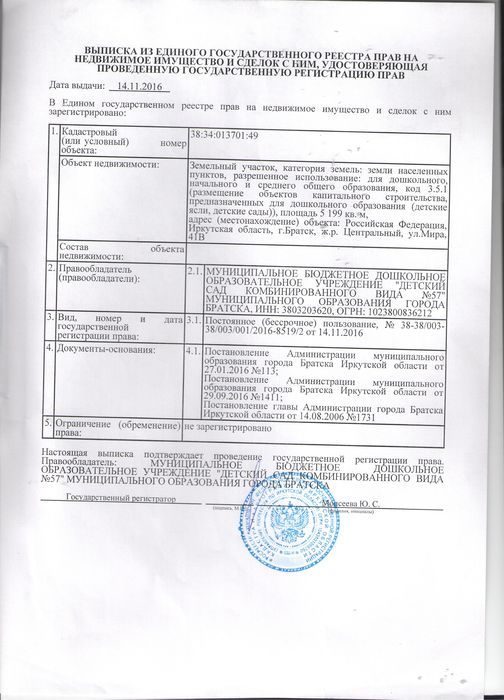

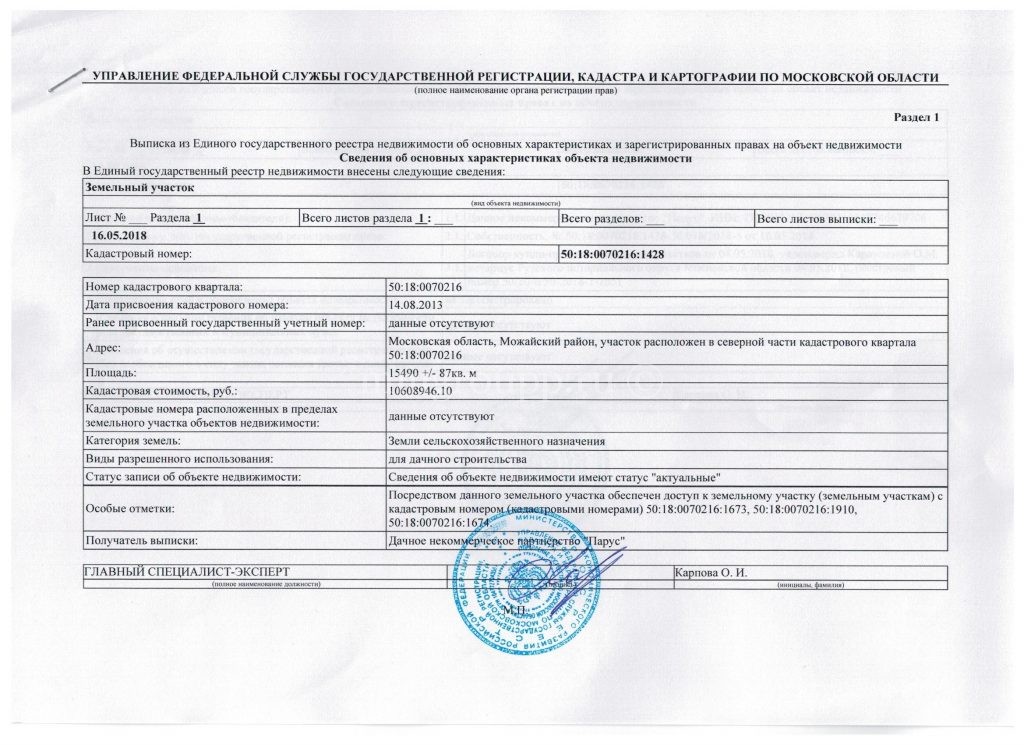

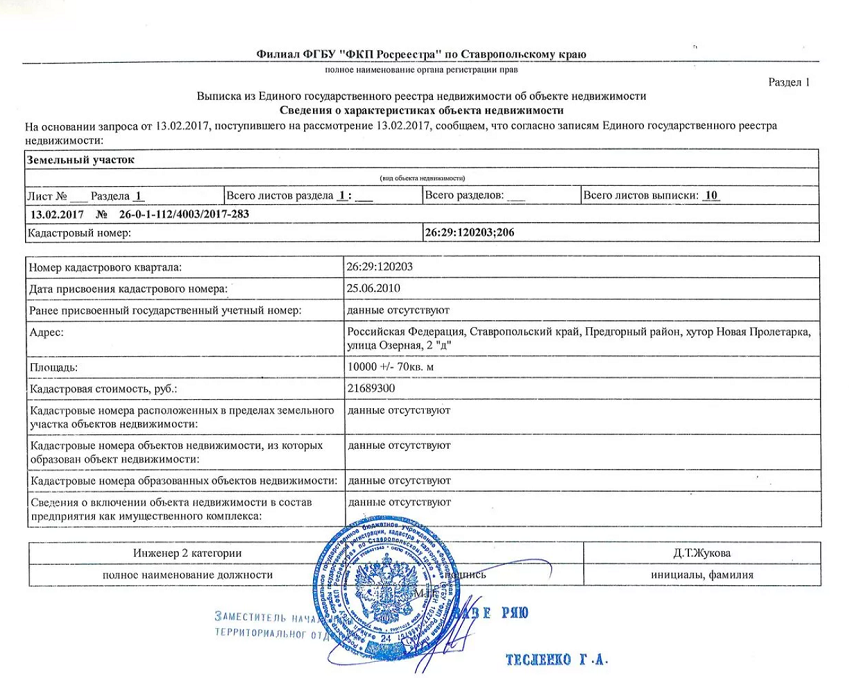

1. Выписка из ЕГРН

онлайн

официальный документ в электронном виде

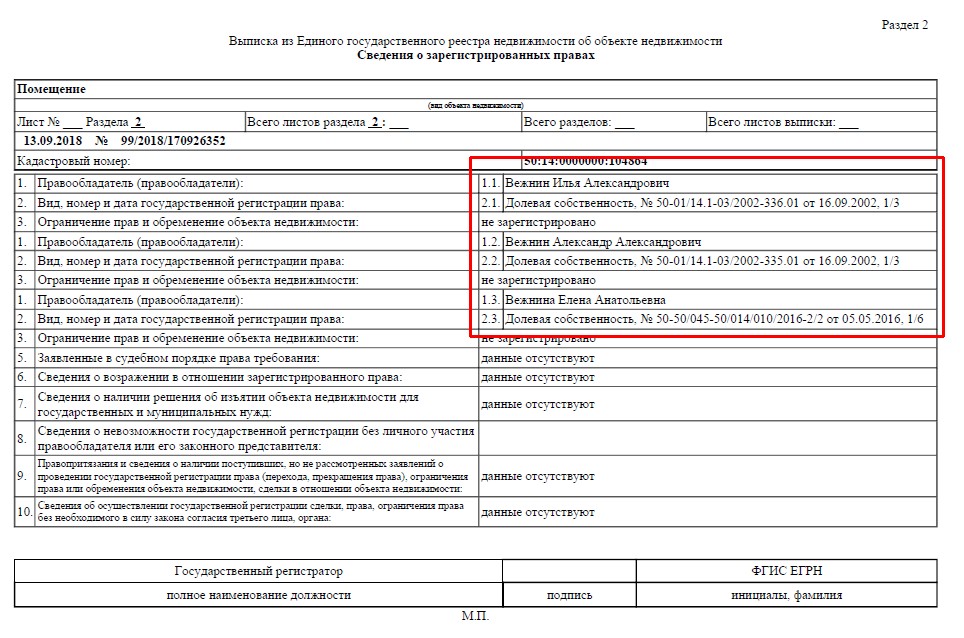

Сведения о правах и обременениях или о переходе прав на объекты недвижимости по всей РФ.

2. Выписка из ЕГРН на бумаге

с печатью

об основных характеристиках и зарегистрированных правах

официальный документ с печатью

Сведения о характеристиках объекта недвижимости, зарегистрированных правах,

ограничениях и обременениях, а также описание местоположения (чертеж, схема).

3. Выписка из ЕГРН

расширенная

об объекте недвижимости (с координатами границ и доп.

ограничениями)

ограничениями)

официальный документ с печатью

Сведения о характеристиках объекта, зарегистрированных правах, ограничениях,

описание местоположения в т.ч. координаты границ и данные о правопритязаниях.

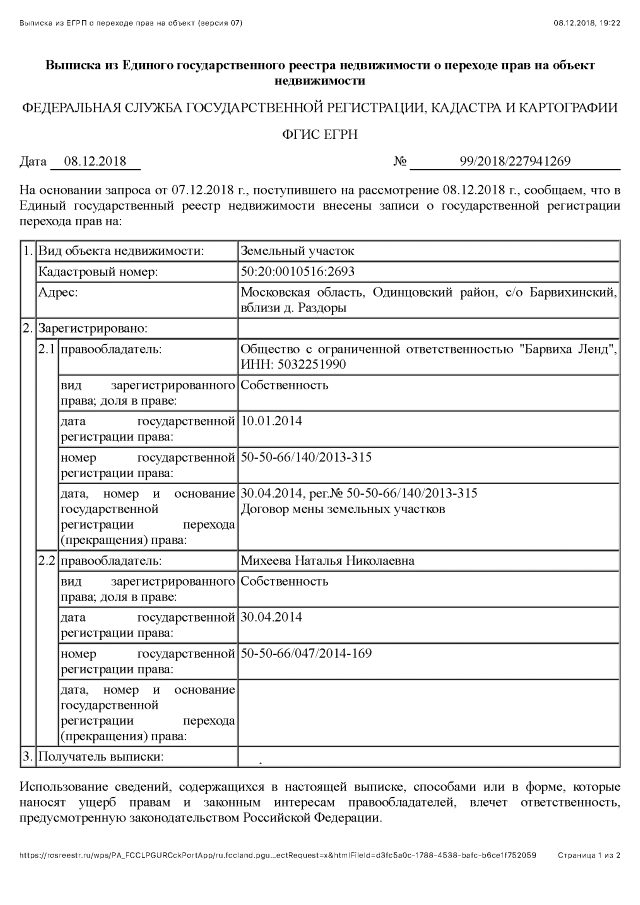

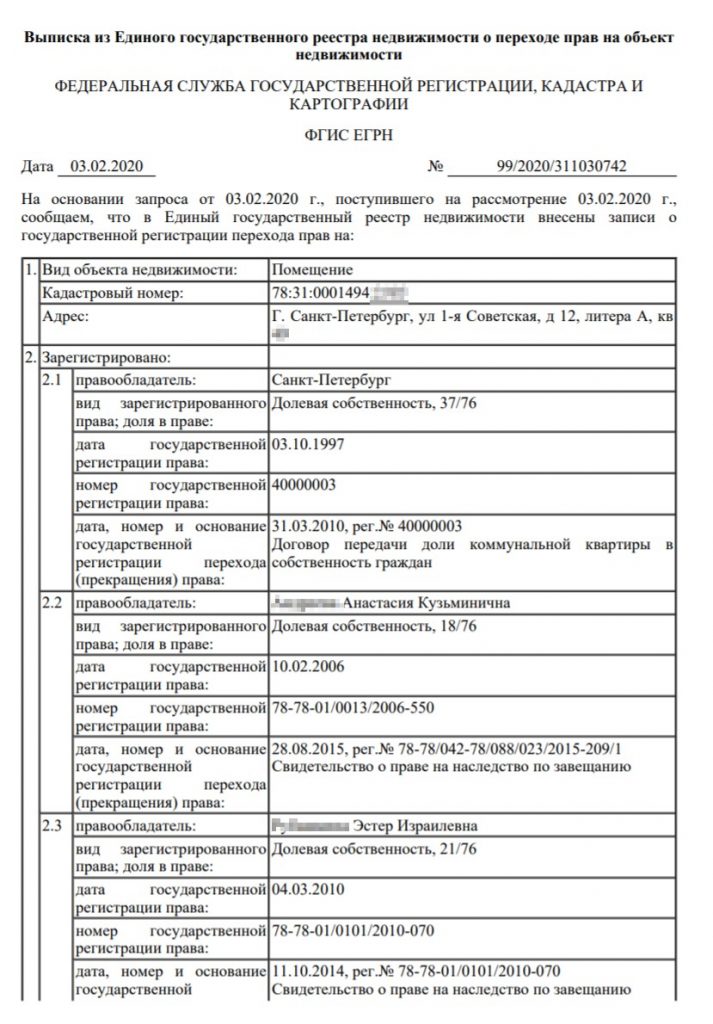

4. Выписка из ЕГРН

о переходе прав

официальный документ с печатью

История перехода прав с 1998 года по н/время. Сведения о правообладателях

(собственниках), документах основания перехода (прекращения) права.

5. Сведения из ЕГРН

(вся история объекта)

документ в электронном виде

Сведения о переходах прав с 1998 года по н/время, документах основания.

История всех ограничений / обременений, дополнительные сведения…

6. Выписка из ЕГРН

о правах отдельного лица

официальный документ с печатью

Сведения об имевшихся и/или имеющихся объектах недвижимости

в собственности конкретного лица с 1998 года по настоящее время.

7. Выписка из ЕГРН

о кадастровой стоимости

официальный документ с печатью

Содержит дополнительные сведения о кадастровой стоимости объекта.

Возможен расчет и указание стоимости на конкретную дату.

8. Выписка из ЕГРН

(ДДУ)

о зарегистрированных договорах участия в долевом строительстве

официальный документ с печатью или электронном виде

Сведения о характеристиках объекта, зарегистрированных правах, ограничениях,

об участниках долевого строительства и зарегистрированных договорах участия.

9. Выписка из ЕГРН

о правоустанавливающих документах

официальный документ с печатью

Сведения о содержании правоустанавливающих документов на основании

которых зарегистрировано право (реквизиты и краткое содержание документа).

10. Выписка из ЕГРН о признании правообладателя

недееспособным или ограниченно дееспособным

официальный документ с печатью или электронном виде

Сведения о том, имеются ли данные в отношении правообладателя

о признании его недееспособным или ограниченно дееспособным.

Заказать услугу

Оформите заявку на сайте, мы свяжемся с вами в ближайшее время и ответим на все интересующие вопросы.

Re: [Обсудить-gnuradio] RSSI (было: Re: Математическая библиотека)

Re: [Обсудить-gnuradio] RSSI (было: Re: Математическая библиотека)

|

[Вверх][Все списки]

Передовой

[Дата Предыдущая][Дата Следующая][Предыдущая Тема][Следующая Тема][Указатель Даты][Указатель Темы]

| Из : | Маркус Мюллер |

| Субъект : | Re: [Discuss-gnuradio] RSSI (было: Re: Математическая библиотека) |

| Дата : | Ср, 19 Мар 2014 12:20:35 +0100 |

| Агент пользователя : | Mozilla/5. 0 (X11; Linux x86_64; rv:24.0) Gecko/20100101 Thunderbird/24.3.0 0 (X11; Linux x86_64; rv:24.0) Gecko/20100101 Thunderbird/24.3.0 |

----- НАЧАТЬ ПОДПИСАННОЕ СООБЩЕНИЕ PGP ----- Хэш: SHA1 Привет, Овенчжан, Добро пожаловать в список рассылки! GRC — это инструмент для построения блок-схем блоков GNU Radio; есть в GRC нет «математической библиотеки», но есть блоки, выполняющие математические операции. Поскольку вы, вероятно, ищете sqrt(|x|²), попробуйте использовать блок «Complex to Mag». В качестве побочного узла, так как эта тема появляется примерно каждые два месяца на этот список рассылки: RSSI не «указывает» ничего конкретного. Ты должна иметь модель для вашего сигнала, чтобы объяснить, что получено мощность сигнала -- это нечто совершенно другое для разные способы передачи. Поэтому никогда не может быть единого система для извлечения RSSI! Привет, Маркус 19.03.2014 10:14, ?? написал: > > Привет! Это первый раз, когда я отправляю электронное письмо в список рассылки GNURadio. > Очень рад обменяться идеями со всеми участниками.> > Недавно я хотел извлечь RSSI из USRP N210. Есть ли > Система для извлечения RSSI, или я должен собрать систему самостоятельно? > > Есть ли в GRC библиотека с математическим модулем для вычисления > квадратный и квадратный корень? > > > наилучшего, пожелания > > Овенчжан > > > > > > > > > ______________________________________________ Обсудить-гнурадио > адрес списка рассылки@скрытый > https://lists.gnu.org/mailman/listinfo/discuss-gnuradio > -----НАЧАТЬ ПОДПИСЬ PGP----- Версия: GnuPG v1 Комментарий: Использование GnuPG с Thunderbird — http://www.enigmail.net/ iQEcBAEBAgAGBQJTKX2CAAoJEAFxB7BbsDrLU54IAIs3CyUPKb/qVKpKuhnxVLja UievSFiExsjl64o5y5RfQ5L/nUgaLGNoxBzAzPqEkKBB2P0YA5NmQAr++6p48iJn xhVTqET2IzcYbAu3LzG+oBF+sT4KC+fcjFxmW/xozLNjwXjSpyyXzI5cU0k+hrFE zLpue+fWt3VPMEKs+5o00tN6nTtw9pVBVbGGsR1ECRiy6MjWAHGyGTn2t8S4n6Gz rWuXDm0FvrvMn9wdEsbnQLFh/vnC0UddhJYPEwa8+fgwaTSsR1Gkq7BPov5WlEYT 87sUVL2pwcEs1N+kbqdlt5Um3ATW2Fmtw+aRZ4n8donf6Wq/HbU0cNM4gkVCOwE= =SGox -----КОНЕЦ ПОДПИСИ PGP-----

| [Предыдущий в теме] | Текущая резьба | [Следующая в теме] |

- [Обсудить-gnuradio] Математическая библиотека , 张文 , 19.

03.2014

03.2014- Re: [Обсудить-gnuradio] RSSI (было: Re: Математическая библиотека) ,

Маркус Мюллер <=

- Re: [Обсудить-gnuradio] RSSI (было: Re: Математическая библиотека) ,

- Предыдущая по дате:

[Обсудить-gnuradio] Математическая библиотека - Далее по дате:

Re: [Обсудить-gnuradio] rx_ofdm не работает после синхронизатора - Предыдущий по теме:

[Обсудить-gnuradio] Математическая библиотека - Далее по теме:

[Обсудить-gnuradio] uhd_rx_cfile: получение постоянных O-переполнения с использованием USRP B200 с debian - Индекс(ы):

- Дата

- Резьба

RFNoC 4 Настройка среды разработки для устройств USRP

Это руководство предназначено для настройки среды радиочастотной сети на кристалле (RFNoC) версии 4 для разработки FPGA на универсальных программных радиопериферийных (USRP) устройствах производства Ettus Research (часть National Instrument). Эти устройства USRP очень часто используются для захвата сигналов глобальной навигационной спутниковой системы (GNSS), такой как глобальная система позиционирования (GPS), GALILEO, ГЛОНАСС, BEIDOU и других.

Эти устройства USRP очень часто используются для захвата сигналов глобальной навигационной спутниковой системы (GNSS), такой как глобальная система позиционирования (GPS), GALILEO, ГЛОНАСС, BEIDOU и других.

Устройство USRP представляет собой универсальное программно определяемое радио (SDR). SDR — это система, которая выполняет многие задачи обработки сигналов в механизме программируемой цифровой обработки сигналов (DSP). Этот механизм DSP через аналого-цифровые (АЦП) и цифро-аналоговые (ЦАП) цепи соединяется с аналоговыми цепями, а затем с антенной для интерфейса с эфиром (каналом связи). Подробное объяснение SDR можно найти в другом месте.

RFNoC — это распределенная по сети платформа инструментов обработки, ориентированная на обеспечение обработки FPGA в устройствах USRP. Основная цель RFNoC — ускорить разработку FPGA на базе хоста, чтобы использовать возможности вычислений FPGA. На рисунке ниже показаны несколько примеров устройств USRP, представляющих собой три основные системы: серии E, X и N 3.

Несколько типов устройств USRP: серии E, X и N 3.

Учебное пособие

есть несколько важных замечаний:

— Целевые устройства — это USRP серии 3: X3xx, E3xx и N3xx

— используется RFNoC 4, который отличается от предыдущей структуры RFNoC 3. Вся разработка ПЛИС для устройств USRP серии 3 должна быть переведена на RFNoC 4. Следовательно, все термины RFNoC в этом документе будут относиться к RFNoC 4.

— термины процессор общего назначения (GPP) и программируемая пользователем решетчатая матрица (FPGA) относятся к системе обработки (PS) и программируемой логике (PL) соответственно в терминологии Xilinx

1. Введение

RFNoC — это платформа обработки для реализации высокогибкой и высокопроизводительной цифровой обработки сигналов (DSP) в программируемой решетчатой матрице (FPGA) для программно-определяемой радиосвязи (SDR) [1]. RFNoC реализован для устройств USRP серии 3 (X3xx, E3xx, N3xx), оснащенных Xilinx серии Kintex-7 (X3xx) или Zynq серии 7000 (N3xx, E3xx). Основная идея RFNoC состоит в том, чтобы обрабатывать все связи между блоками на основе стандарта AMBA AXI4 и позволить пользователям сосредоточиться на разработке своей логики HDL и гибко конфигурировать свои блоки и всю архитектуру FPGA [1,2]. В FPGA блок относится к блоку интеллектуальной собственности (IP), в котором логика обработки реализована на определенных языках описания оборудования (HDL), например, Verilog и VHDL [8,9].]. Все UHD API вызывают блок RFNoC под капотом .

Основная идея RFNoC состоит в том, чтобы обрабатывать все связи между блоками на основе стандарта AMBA AXI4 и позволить пользователям сосредоточиться на разработке своей логики HDL и гибко конфигурировать свои блоки и всю архитектуру FPGA [1,2]. В FPGA блок относится к блоку интеллектуальной собственности (IP), в котором логика обработки реализована на определенных языках описания оборудования (HDL), например, Verilog и VHDL [8,9].]. Все UHD API вызывают блок RFNoC под капотом .

Рисунок 1: Общая структура RFNoC 4 для устройств SDR на основе USRP [2].

На рис. 1 схематично показана структура RFNoC. На рисунке 1 структура RFNoC автоматически генерирует NoC Core (пунктирная рамка), а пользователи несут ответственность за блоки NoC (часть пользовательской логики или пользовательский IP-блок ). В фреймворке есть два типа транспорта между блоками: транспорт данных и транспорт управления :

· Передача данных

Перемещение высокоскоростных данных с малой задержкой между блоками. Этот транспорт поддерживает детерминированную и синхронизированную потоковую передачу данных с необязательным включением встроенных метаданных. Этот транспорт данных должен быть подключен через маршрутизацию, статическую или динамическую, между блоками .

Этот транспорт поддерживает детерминированную и синхронизированную потоковую передачу данных с необязательным включением встроенных метаданных. Этот транспорт данных должен быть подключен через маршрутизацию, статическую или динамическую, между блоками .

o Динамическая маршрутизация: при этой маршрутизации маршрут данных между блоками может быть переконфигурирован во время выполнения. Однако эта конфигурация требует значительно больше ресурсов FPGA, чем статическая маршрутизация.

o Статическая маршрутизация: в этой маршрутизации блоки маршрутизируются статически и могут быть настроены только во время выполнения и не являются гибкими. Однако для этого требуется лишь значительный небольшой ресурс ПЛИС.

· Управление транспортом

Движение с низкой скоростью и высокой задержкой транзакционных данных, таких как пользовательский регистр . Этим типом данных может быть, например, состояние блока или состояние управления. Существует три типа основных транзакционных процессов: чтение регистра, запись регистра и ожидание шины. Все блоки связаны друг с другом для этого управляющего транспорта через панель управления на рисунке 1, так что каждый блок может отправлять управляющее сообщение любым блокам. Маршрутизация этого управляющего транспорта может быть эффективно реализована в FPGA (поскольку она не требует высокой пропускной способности и низкой задержки).

Существует три типа основных транзакционных процессов: чтение регистра, запись регистра и ожидание шины. Все блоки связаны друг с другом для этого управляющего транспорта через панель управления на рисунке 1, так что каждый блок может отправлять управляющее сообщение любым блокам. Маршрутизация этого управляющего транспорта может быть эффективно реализована в FPGA (поскольку она не требует высокой пропускной способности и низкой задержки).

· Дополнительный внешний транспорт для транспортировки внешних данных в/из ПЛИС (дополнительно).

Ядро NoC (рис. 1) состоит из четырех основных частей:

· Перемычка CHDR

Перемычка CHDR — это шина для передачи данных с высокой пропускной способностью и малой задержкой. Эта шина настроена на 64 бита и предназначена для поддержки потока данных с высокой пропускной способностью.

· Конечная точка потока

Конечная точка потока — это место, где начинаются и заканчиваются все потоки данных в секции FPGA, а также интерфейс к/от GPP через транспортные блоки. Любые блоки IP, подключенные к конечной точке потока, могут подключаться друг к другу. Подключение IP-блоков к конечной точке потока — это стратегия динамической маршрутизации между блоками, где топологии блоков могут быть установлены по желанию и во время выполнения. Однако для этой стратегии динамической маршрутизации требуются более значительные ресурсы FPGA, чем для стратегии статической маршрутизации .

Любые блоки IP, подключенные к конечной точке потока, могут подключаться друг к другу. Подключение IP-блоков к конечной точке потока — это стратегия динамической маршрутизации между блоками, где топологии блоков могут быть установлены по желанию и во время выполнения. Однако для этой стратегии динамической маршрутизации требуются более значительные ресурсы FPGA, чем для стратегии статической маршрутизации .

· Управляющая поперечина

Управляющая поперечина обеспечивает маршрутизацию от и ко всем блокам для передачи управления (данные пользовательского регистра). Он автоматически строится в ядре NoC. Следовательно, мы можем отправить пользовательский регистр в любой блок в FPGA

· Статический маршрутизатор

Статический маршрутизатор предназначен для статического соединения блоков в FPGA. Все блоки, подключенные через статический маршрутизатор, имеют маршрут исправления, сгенерированный во время компиляции. Это соединение является самым быстрым маршрутом данных между блоками и требует меньше ресурсов FPGA, чем динамическая маршрутизация. Однако, если мы хотим изменить конфигурацию маршрутизации между блоками, нам нужно ресинтезировать (перекомпилировать) HDL и записать его на FPGA.

Однако, если мы хотим изменить конфигурацию маршрутизации между блоками, нам нужно ресинтезировать (перекомпилировать) HDL и записать его на FPGA.

2. Установка среды разработки RFNoC

Для установки среды RFNoC нам необходимо установить определенную версию библиотек Vivado , UHD , GNU Radio и Gr-Ettus . Установка должна производиться последовательно. Для RFNoC 4 требуется Ubuntu 20.04-LTS . Рекомендуется, чтобы общий объем свободного места на жестком диске, на котором будет выполняться установка, был > 100 ГБ . Перед проведением установки нам нужно установить оболочку по умолчанию на BASH (по умолчанию Ubuntu использует DAHS в качестве оболочки по умолчанию) [3] по:

$ sudo dpkg-reconfigure dash Выберите «Нет», затем $ ll /бин/шт.

Шаги установки следующие:

2.0 Установка зависимостей

Необходимо установить все необходимые зависимости для установки Vivado, UHD, GNU Radio и GR-Ettus [4]. Зависимости Thess включают libtinfo5 и libncurses5, которые необходимы при установке Vivado 2019..1. Установку можно выполнить с помощью:

Зависимости Thess включают libtinfo5 и libncurses5, которые необходимы при установке Vivado 2019..1. Установку можно выполнить с помощью:

sudo apt install git cmake g++ libboost-all-dev libgmp-dev swig \ python3-numpy python3-mako python3-sphinx python3-lxml \ doxygen libfftw3-dev libsdl1.2-dev libgsl-dev libqwt-qt5-dev \ libqt5opengl5-dev python3-pyqt5 liblog4cpp5-dev libzmq3-dev \ python3-yaml python3-click python3-click-plugins python3-zmq \ python3-scipy python3-gi python3-gi-cairo gobject-introspection \ gir1.2-gtk-3.0 build-essential libusb-1.0-0-dev python3-docutils \ python3-setuptools python3-ruamel.yaml python-is-python3 \ libtinfo5 libncurses5

2.1 Установка Vivado System Suite 2019.1

Перед установкой Vivado нам необходимо переименовать интернет-адаптер в eth0 (Xilinx Vivado License Manager ищет адаптер Ethernet с именем «eth0»)[5]:

1 .Создать файлы: 70-persistent-net.rules в этой директории /etc/udev/rules. d/

d/

2. Добавить в файл эту строку (подставить xx:xx:xx:xx:xx:xx на наш MAC-адрес, можем проверить командой ifconfig ):

SUBSYSTEM=="net", ACTION=="добавить", DRIVERS=="?*", ATTR{адрес}=="xx:xx:xx:xx:xx:xx", ATTR{dev_id}==" 0x0", ATTR{type}=="1", NAME="eth0" 3. Затем перезапустите Linux.

Версия Vivado, которую нам нужно установить, — Vivado 2019.1. Мы рекомендуем следовать этой видеоинсталляции [6]. Эту версию Vivado можно загрузить с веб-сайта Xilinx [7]. С веб-сайта мы также можем загрузить лицензию веб-пакета Vivado, чтобы иметь возможность запускать синтезатор HDL для E312.

Примечание:

· Нам необходимо установить System Suite версии , чтобы иметь возможность запустить тестовый стенд (лицензия Vivado требуется только тогда, когда мы хотим синтезировать наш HDL)

· Для E312 мы можем использовать Vivado лицензия веб-пакета (при установке пакета проектирования системы) бесплатно для запуска синтезатора HDL и создания файла битового потока FPGA.

2.2 Установка UHD 4

UHD 4.0 содержит структуру RFNoC и может быть установлен:

git clone --branch UHD-4.0 https://github.com/ettusresearch/uhd.git uhd mkdir uhd/хост/сборка; cd uhd/хост/сборка сделай .. делать sudo make install

2.3 Установка GNU Radio 3.8

GNU Radio 3.8 можно установить с помощью:

git clone --branch maint-3.8 --recursive https://github.com/gnuradio/gnuradio.git gnuradio mkdir gnuradio/сборка; cd gnuradio/сборка; сделай .. делать sudo make install

2.4 Установка Gr-Ettus

Gr-Ettus требуется, особенно если мы хотим интегрировать наш RFNoC только в GNU Radio Companion (GRC). Однако, даже если мы не хотим интегрировать наш RFNoC в GRC, нам все равно потребуется установить эту библиотеку, чтобы использовать rfnocmodtool (программное обеспечение на основе Python) для создания нашей среды разработки RFNoC. rfnocmodtool — это инструмент для создания папки проекта разработки RFNoC и файлов скелета проекта . Gr-Ettus можно установить:

Gr-Ettus можно установить:

git clone --branch maint-3.8-uhd4.0 https://github.com/ettusresearch/gr-ettus.git gr-ettus mkdir gr-ettus/сборка; cd gr-ettus/сборка; cmake -DENABLE_QT=Истина .. делать судо сделать установить

Примечание:

· Установка GNU Radio и Gr-Ettus по-прежнему требуется, хотя мы не будем использовать интеграцию GNU Radio Companion. Однако это радио GNU требуется для Gr-Ettus, а Gr-Ettus требуется для rfnocmodtool .

3. Создание среды разработки RFNoC

Для создания среды разработки RFNoC, то есть для создания файлов проекта и скелета, мы используем rfnocmodtool. Чтобы использовать rfnocmodtool в терминале оболочки, нам нужно экспортировать путь rfnocmodtool в терминальную среду:

экспорт PYTHONPATH=/usr/local/lib/python3/dist-packages/:$PYTHONPATH затем, sudo ldconfig

для создания нового модуля RFNoC (новый проект), это можно сделать с помощью:

rfnocmodtool newmod

вставьте «ProjectName», и он создаст папку «rfnoc-ProjectName» в активном каталоге.

Рисунок 2: Папка проекта, созданная после выполнения команды rfnocmodtool newmod. Наиболее важными папками для разработки наших пользовательских блоков RFNoC и IP являются папки rfnoc, include и lib.

На рис. 2 показана созданная папка проекта разработки RFNoC после запуска rfnocmodtool newmod. На рисунке 2 показаны три папки, наиболее важные для разработки RFNoC: папки rfnoc, include и lib. Папка rfnoc содержит всю необходимую папку для создания нашего собственного пользовательского блока IP и для настройки нашего пользовательского блока и кода RFNoC. Пользовательский блок IP создается сгенерированным каркасом Verilog, а файл тестового стенда — сгенерированными системными файлами Verilog. Между тем, включают и папки lib содержат заголовок и файл реализации C++ для нашего пользовательского контроллера блока для доступа к нашему блоку через C++ UHD API.

На рис. 3 показаны автоматически сгенерированные папки подпроектов внутри папки rfnoc (рис. 2). Есть три подпапки: блоков, fpga и папки icores. Папка блоков содержит файл YAML для настройки наших пользовательских блоков IP, а папка icores содержит файл YAML для настройки ядра NOC в разработанном RFNoC. Наконец, папка fpga содержит автоматически сгенерированную папку блока FPGA (формат имени папки — rfnoc_block_BLOCKNAME). Эта папка блока FPGA содержит файлы скелета для наших пользовательских блоков IP, где пользовательская логика находится в Verilog, а пользовательский тестовый стенд — в системном Verilog. Изначально папка fpga не содержит папки блока FPGA, пока мы не создадим собственную разработку блока, то есть добавим новый блок NOC в разрабатываемый RFNoC.

2). Есть три подпапки: блоков, fpga и папки icores. Папка блоков содержит файл YAML для настройки наших пользовательских блоков IP, а папка icores содержит файл YAML для настройки ядра NOC в разработанном RFNoC. Наконец, папка fpga содержит автоматически сгенерированную папку блока FPGA (формат имени папки — rfnoc_block_BLOCKNAME). Эта папка блока FPGA содержит файлы скелета для наших пользовательских блоков IP, где пользовательская логика находится в Verilog, а пользовательский тестовый стенд — в системном Verilog. Изначально папка fpga не содержит папки блока FPGA, пока мы не создадим собственную разработку блока, то есть добавим новый блок NOC в разрабатываемый RFNoC.

Чтобы добавить новый пользовательский блок NOC (блок FPGA), перейдите в папку созданного проекта RFNoC. Это можно сделать:

cd rfnoc-ProjectName

, а затем введите

rfnocmodtool add

, вставьте «BlockName», и он создаст папку rfnoc_block_BlockName в папке rfnoc (рис. 2).

2).

Примечание:

· Чтобы просмотреть все возможные параметры команды rfnocmodtool, введите

rfnocmodtool help

· Чтобы удалить пользовательский блок NOC (пользовательский блок IP), мы можем использовать команду rfnocmodtool remove

Рисунок 3: Внутри папки rfnoc (см. рисунок 2), созданной с помощью rfnocmodtool add. Рисунок 4: Внутри папки fpga (см. рисунок 3). В этом примере мы вводим имя блока « усиления » при использовании команды rfnocmodtool add. Внутри папки мы можем найти коды Verilog для пользовательской логики и испытательного стенда

. На рис. 4 показан пример автоматически созданной папки подпроекта, когда мы создаем новый пользовательский блок IP с именем Gain с помощью команды rfnocmodtool add. Следовательно, папка подпроекта, созданная в папке fpga (см. рисунок 3), называется rfnoc_block_gain. Внутри этого блока будет три автоматически сгенерированных файла для реализации пользовательской логики (в Verilog), пользовательского тестового стенда (в System Verilog) и оболочки NOC для пользовательского блока IP (в Verilog). В этом примере файл пользовательской логики — rfnoc_block_gain.v, пользовательский тестовый стенд — rfnoc_block_gain_tb.sv, а файл оболочки NOC — noc_shell_gain.v (9).0224 обратите внимание, что «gain» — это имя пользовательского блока, который мы создали до ).

В этом примере файл пользовательской логики — rfnoc_block_gain.v, пользовательский тестовый стенд — rfnoc_block_gain_tb.sv, а файл оболочки NOC — noc_shell_gain.v (9).0224 обратите внимание, что «gain» — это имя пользовательского блока, который мы создали до ).

4. Разработка индивидуального IP-блока

При разработке пользовательского IP-блока основное внимание уделяется файлам HDL (verilog и системный verilog) внутри папок блоков в папке fpga (рис. 3) и файлам YAML, каждый из которых соответствует созданным пользовательским блокам, внутри папка блока (рис. 3). Мы обсудим конфигурацию файла YAML позже в разделе разработки RFNoc.

Обычно мы просто фокусируемся на файлах YAML (BLOCK_NAM.yml), rfnoc_block_BLOACK_NAME.v и rfnoc_block_BLOCK_NAME_tb.sv. Noc_shell_BLOCK_NAME.v можно изменить, если мы хотим настроить поведение передачи данных от и к нашему пользовательскому блоку IP (что в большинстве случаев не выполняется).

На рис. 5 показан пример YAML-файла блока усиления, созданного с помощью rfnocmodtool add. Ниже приведены пояснения к примеру файла YAMl на рисунке 5 (см. [1]). Идентификатор NOC автоматически генерируется при создании блока. Однако мы можем вставить идентификатор вручную. chdr_width — разрядность кроссбада CHDR (рис. 1).

Ниже приведены пояснения к примеру файла YAMl на рисунке 5 (см. [1]). Идентификатор NOC автоматически генерируется при создании блока. Однако мы можем вставить идентификатор вручную. chdr_width — разрядность кроссбада CHDR (рис. 1).

Секция clock содержит имена часов, которые необходимы в блоке и будут использоваться для подключения от источников часов. rfnoc_chdr и rfnoc_ctrl являются обязательными именами часов (имя не может быть изменено), а ce — определяемыми пользователем часами (имя может быть изменено). Кроме того, мы можем установить допустимый диапазон рабочих часов для каждого имени часов. основных разделов управление и данные секций. Управление содержит опции или настройки для шины управления, а данные содержат опции или настройки для шины данных, включая количество и имя входных и выходных портов в блоке.

Дополнительные разделы (не показаны в этом примере) для расширенной функции: раздел io_port для связи внешнего блока с внешними входами/выходами, раздел регистров для перечисления всех дополнительных пользовательских регистров (помимо одного пользовательского регистра по умолчанию, установленного, когда мы cretae dблок) в блоке и раздел свойств для перечисления всех свойств пользователя блокировки.

Рисунок 5: Пример файла YAML в папке блоков (см. рисунок 4). В этом примере мы вводим имя блока « усиления » при использовании команды rfnocmodtool add.

Чтобы начать разработку собственной логики, мы можем вставить нашу логику в файл rfnoc_block_BLOCK_NAME.v. На рис. 6 показан раздел файла verlilog, в который мы можем вставить собственную пользовательскую логику для разработки пользовательского блока IP. Этот лофик-раздел пользователя находится в конце файла verilog. В файле сгенерированы переменные по умолчанию, которые являются переменными для пользователя 9.0140 выборочные данные и контекстные данные . В большинстве случаев это выборочные данные, которые мы хотим обработать с помощью нашей собственной логики. Переменная входных выборочных данных — m_in_payload_tdata, а переменная выходных данных — s_out_payload_tdata («m» относится к ведущему, а «s» — к ведомому, чтобы соответствовать терминологии Xilinx [9]).

Рисунок 6: Раздел, в который мы вставляем нашу пользовательскую логику в сгенерированном скелетном файле Verilog из команды rfnocmodtool add.

Чтобы проверить нашу пользовательскую логику, мы можем изменить файл rfnoc_block_BLOCK_NAME_tb.sv. На рис. 7 показан автоматически сгенерированный файл каркасного тестового стенда. Чтобы вставить нашу собственную логику тестирования, мы можем отредактировать или вставить код в раздел основного процесса тестирования (как показано на рисунке 7). В этом тестовом разделе есть несколько тестовых кодов по умолчанию, сгенерированных rfnocmodtool, когда мы создаем или добавляем блок. Каждая тестовая логика в основном разделе процесса тестирования находится внутри начало и конец раздела .

Стоит отметить, что в некоторых ситуациях может быть сложно, если вообще возможно, вставить нашу пользовательскую логику тестирования в тестовый стенд. В этой ситуации мы можем пропустить тест, и нам не нужно редактировать или изменять тестовый файл по умолчанию.

Следующим шагом является сборка (компиляция и запуск) файла Verilog пользовательской логики и файла Verilog системы тестового стенда. Чтобы выполнить процесс сборки, мы создаем папку сборки внутри созданной папки проекта (формат имени папки проекта — rfnoc-MOUDLE_NAM). Из этой папки сборки набираем:

Чтобы выполнить процесс сборки, мы создаем папку сборки внутри созданной папки проекта (формат имени папки проекта — rfnoc-MOUDLE_NAM). Из этой папки сборки набираем:

cmake -DUHD_FPGA_DIR=~/uhd/fpga ..

Эта команда предполагает, что папка проекта RFNoC, сгенерированная командой rfnocmodtol newmod, находится в домашнем каталоге (~). После процесса сборки мы можем скомпилировать и запустить файлы пользовательской логики и тестового стенда, а также синтезировать образ RFNoC (ядро NOC, как показано на рисунке 1).

Рисунок 7: Раздел, в который мы вставляем наш пользовательский логический испытательный стенд в сгенерированный скелетный файл System Verilog из команды rfnocmodtool add.

Обратите внимание, что после запуска «cmake -DUHD_FPGA_DIR=~/uhd/fpga ..» мы делаем make и make install только в том случае, если хотим интегрироваться с программным обеспечением GNC. Он будет скомпилирован в libgnuradio-PROJECTNAME.so и некоторые файлы python *. pyc и *.pyo и некоторые другие файлы, например. SWIG и т. д., необходимые для интеграции GRC.

pyc и *.pyo и некоторые другие файлы, например. SWIG и т. д., необходимые для интеграции GRC.

Чтобы скомпилировать код Verilog (HDL) и запустить тестовый стенд [8,9] (для проверки логики нашего пользовательского блока), из папки сборки введите:

make rfnoc_block_BlockName_tb

Эта команда скомпилирует файлы пользовательской логики и тестового стенда и запустит тестовый стенд. Любые ошибки компиляции, обнаруженные в файлах Verilog пользовательской логики, будут показаны в результатах выполнения команды.

5. Разработка индивидуального образа RFNoC

Наконец, после разработки нашего пользовательского блока IP, содержащего нашу собственную пользовательскую логику, мы вставим пользовательский блок в общую конфигурацию RFNoC. Эта конфигурация RFNoC будет синтезирована и прошита на устройствах USRP серии 3. На этом этапе мы также настраиваем маршрутизацию блока в ядре NOC либо статически (меньше ресурсов FPGA и менее гибко), либо динамически (больше ресурсов FPGA и более гибко). Также нам необходимо подключить источник часового домена к блокам NOC в конфигурации RFNoC.

Также нам необходимо подключить источник часового домена к блокам NOC в конфигурации RFNoC.

Для разработки и настройки RFNoC мы модифицируем файл FILENAME_rfnoc_image_core.yml, созданный командой rfnocmodtool newmod. На рисунке 8 показан типичный файл YAML для разработки RFNoC. Объяснения файла YAML следующие. Мы можем добавить конечные точки потока в конечные точки потока и блоки NOC (либо блок по умолчанию из UHD, либо наши пользовательские блоки) в список раздела noc_blocks . В списке соединений раздел настраиваем маршрутизацию нашего блока либо статически, либо динамически. Статическая маршрутизация — это маршрут, который явно упоминается в этом разделе статического соединения. Однако, чтобы сделать маршрутизацию динамической, мы должны создать статическое соединение от конечной точки потока к блоку NOC и сформировать этот блок NOC обратно к конечной точке потока. Поскольку все, что подключено к конечной точке потока, может подключаться к любой конечной точке потока через перемычку CHDR (рис. 1), то с помощью этой стратегии мы создаем динамическое соединение между блоками (см. раздел 1). Стоит отметить, что для создания этих «динамических» соединений потребуется значительно больше ресурсов FPGA, чем для простой статической маршрутизации (в некоторых случаях мы можем не вписать образ RFNoC в устройство USRP FPGA). Наконец, в clk_domains подключаем источники тактирования ко всем блокам NOC в конфигурации RFNoC.

1), то с помощью этой стратегии мы создаем динамическое соединение между блоками (см. раздел 1). Стоит отметить, что для создания этих «динамических» соединений потребуется значительно больше ресурсов FPGA, чем для простой статической маршрутизации (в некоторых случаях мы можем не вписать образ RFNoC в устройство USRP FPGA). Наконец, в clk_domains подключаем источники тактирования ко всем блокам NOC в конфигурации RFNoC.

ПРИМЕЧАНИЕ. , чтобы иметь возможность генерировать этот xxx_rfnoc_image_code , нам нужно создать хотя бы один блок rfnoc с помощью rfnocmodtool добавить команду синтеза 901, даже если мы не используем 902 этот блок. разработан RFNoC блок из папки сборки :

make FILENAME_rfnoc_image_core

Этот процесс синтеза займет некоторое время (обычно один час в зависимости от ресурса ЦП). На этом этапе размер нашей разработки RFNoC будет сравниваться с емкостью FPGA целевого устройства USRP. Если размер RFNoC больше емкости FPGA, произойдет ошибка. Кроме того, на этом этапе синтеза также отображаются ошибки, если в коде Verilog нашей пользовательской логики есть логическая ошибка.

Если размер RFNoC больше емкости FPGA, произойдет ошибка. Кроме того, на этом этапе синтеза также отображаются ошибки, если в коде Verilog нашей пользовательской логики есть логическая ошибка.

В случае успеха синтезированный битовый поток (образ RFNoC) генерируется в UHDInstallPath /uhd/fpga/usrp3/top/ x3xx /build Где UHDInstallPath — это путь установки UHDInstallPath commonHome), а x3xx — тип используемого нами устройства USRP 3.

На рис. 9 показан пример результатов сборки. Есть три файла с расширением *.bit, *. ДТС, *. рпт. Файл *.bit — это файл потока битов, содержащий двоичный файл изображения RFNoC. Два других файла также требуются, когда мы загружаем изображение на целевое устройство (9).0224 эти два *. ДТС и *. Файлы rpt должны всегда находиться в той же папке, что и файл *.bit для процесса загрузки ).

Рисунок 8: Пример файла YAML в папке icores (см. рисунок 2) для настройки RFNoC: включенные блоки, тип соединения и настройки домена часов. Рисунок 9: Пример результатов сборки для синтеза изображения RFNoC для USRP Серия E3xx.

Рисунок 9: Пример результатов сборки для синтеза изображения RFNoC для USRP Серия E3xx.

6. Загрузка настроенного образа RFNoC в устройство USRP

Наконец, после успешного процесса синтеза нашего образа RFNoC нам необходимо загрузить образ синтеза (файл битового потока) в целевые устройства USRP.

Для E312 (при условии, что мы находимся в папке, содержащей файл *.bit):

uhd_image_loader --args="type=e3xx" --fpga-path=./filename.bit

Проверить, выполняется ли синтез RFNoC образ успешно загружен в целевое устройство ISRP, введите:

uhd_usrp_probe

На рис. 10 показан пример успешной прошивки образа RFNoC в устройство e312 USRP. На рисунке 10 показаны все блоки NOC, включенные в файл icore YAML (рисунок 8), и их соединения.

Рисунок 10: Пример перечисленных блоков и их соединений в устройстве USRP E312 после выполнения команды uhd_usrp_probe.

Стоит отметить, что, хотя наш пользовательский образ RFNoC (битовый файл) может быть синтезирован, если в конфигурации RFNoC есть ошибка или ошибка (которая нарушает правила структуры RFNoC) , uhd_usrp_probe выдаст ошибку в процессе зондирования.

Ссылки

[1] RFNoC 4 Версия спецификации 1 https://files.ettus.com/app_notes/RFNoC_Specification.pdf

[2] Начало работы с RFNoC в UHD 4.0 https://kb.ettus.com/Getting_Started_with_RFNoC_in_UHD_4.0

[3] Начало работы с RFNoC Development https://kb.ettus.com/Getting_Started_with_RFNoC_Development

[4] ] Руководство по миграции RFNoC 4 https://kb.ettus.com/RFNoC_4_Migration_Guide

[5] RFNoC https://kb.ettus.com/RFNoC

[6] Видео Youtube о том, как установить Xilinx Vivado https:// www.youtube.com/watch?v=iwVd4TIB0ME&t=1525s

[7] Xilinx Vivado 2019.1 https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools/archive.html

[8] Юнсалан, К. и Тар, Б. ., 2017. Проектирование цифровых систем с FPGA: реализация с использованием Verilog и VHDL. Образование Макгроу-Хилл.

[9] Крокетт, Л.Х., Эллиот, Р., Эндервитц, М. и Стюарт, Р., 2014. Книга Zynq: встроенная обработка с Arm Cortex-A9 на Xilinx Zynq-7000 All Programmable Soc.

>

> Недавно я хотел извлечь RSSI из USRP N210. Есть ли

> Система для извлечения RSSI, или я должен собрать систему самостоятельно?

>

> Есть ли в GRC библиотека с математическим модулем для вычисления

> квадратный и квадратный корень?

>

>

> наилучшего, пожелания

>

> Овенчжан

>

>

>

>

>

>

>

>

> ______________________________________________ Обсудить-гнурадио

> адрес списка рассылки@скрытый

> https://lists.gnu.org/mailman/listinfo/discuss-gnuradio

>

-----НАЧАТЬ ПОДПИСЬ PGP-----

Версия: GnuPG v1

Комментарий: Использование GnuPG с Thunderbird — http://www.enigmail.net/

iQEcBAEBAgAGBQJTKX2CAAoJEAFxB7BbsDrLU54IAIs3CyUPKb/qVKpKuhnxVLja

UievSFiExsjl64o5y5RfQ5L/nUgaLGNoxBzAzPqEkKBB2P0YA5NmQAr++6p48iJn

xhVTqET2IzcYbAu3LzG+oBF+sT4KC+fcjFxmW/xozLNjwXjSpyyXzI5cU0k+hrFE

zLpue+fWt3VPMEKs+5o00tN6nTtw9pVBVbGGsR1ECRiy6MjWAHGyGTn2t8S4n6Gz

rWuXDm0FvrvMn9wdEsbnQLFh/vnC0UddhJYPEwa8+fgwaTSsR1Gkq7BPov5WlEYT

87sUVL2pwcEs1N+kbqdlt5Um3ATW2Fmtw+aRZ4n8donf6Wq/HbU0cNM4gkVCOwE=

=SGox

-----КОНЕЦ ПОДПИСИ PGP-----

>

> Недавно я хотел извлечь RSSI из USRP N210. Есть ли

> Система для извлечения RSSI, или я должен собрать систему самостоятельно?

>

> Есть ли в GRC библиотека с математическим модулем для вычисления

> квадратный и квадратный корень?

>

>

> наилучшего, пожелания

>

> Овенчжан

>

>

>

>

>

>

>

>

> ______________________________________________ Обсудить-гнурадио

> адрес списка рассылки@скрытый

> https://lists.gnu.org/mailman/listinfo/discuss-gnuradio

>

-----НАЧАТЬ ПОДПИСЬ PGP-----

Версия: GnuPG v1

Комментарий: Использование GnuPG с Thunderbird — http://www.enigmail.net/

iQEcBAEBAgAGBQJTKX2CAAoJEAFxB7BbsDrLU54IAIs3CyUPKb/qVKpKuhnxVLja

UievSFiExsjl64o5y5RfQ5L/nUgaLGNoxBzAzPqEkKBB2P0YA5NmQAr++6p48iJn

xhVTqET2IzcYbAu3LzG+oBF+sT4KC+fcjFxmW/xozLNjwXjSpyyXzI5cU0k+hrFE

zLpue+fWt3VPMEKs+5o00tN6nTtw9pVBVbGGsR1ECRiy6MjWAHGyGTn2t8S4n6Gz

rWuXDm0FvrvMn9wdEsbnQLFh/vnC0UddhJYPEwa8+fgwaTSsR1Gkq7BPov5WlEYT

87sUVL2pwcEs1N+kbqdlt5Um3ATW2Fmtw+aRZ4n8donf6Wq/HbU0cNM4gkVCOwE=

=SGox

-----КОНЕЦ ПОДПИСИ PGP-----

03.2014

03.2014